## 优化芯片开发生命周 期

半导体芯片的市场化过程变得越来越复杂和成本高昂。为了加快产品推向市场的速度并确保首次生产的质量,芯片企业正在不断改进他们的流程。这对于项目的盈利性至关重要,因为任何错误或延误都可能导致数千万甚至数亿美元的研发成本和潜在收入损失。

# EDA工具:驱动半导体设计流程

在半导体和电子行业的集成电路以及电子系统的设计、测试和制造过程中,EDA(电子设计自动化)软件扮演着核心角色。这些工具通过进行仿真、布局、验证和综合等电子设计的关键步骤,协助工程师实现高效且精确的芯片设计。

## EDA流程中的挑战

- **存储数据** 对于复杂芯片设计,EDA可能会 生成数百TB的数据。

- **仿真运行时间** 随着芯片设计复杂性的增加,CPU和存储IO的压力也随之加大,导致 仿真运行所需时间延长,并增加了运行过程 中中断或失败的可能性,迫使重新启动。

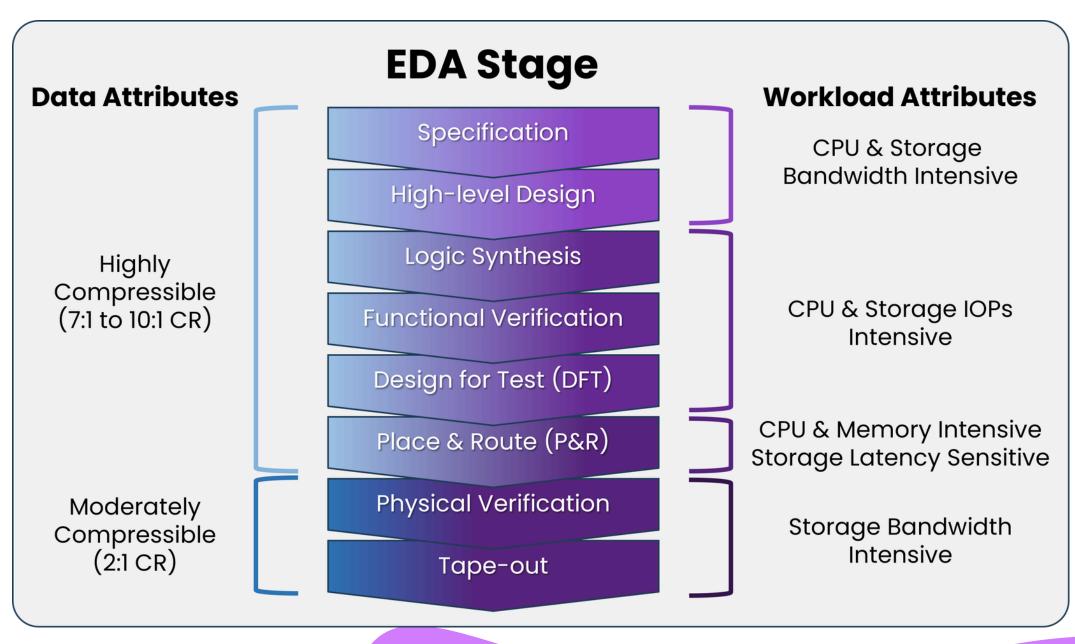

- 工作负载的变化 EDA流程各阶段的工作负载在对CPU、内存和存储的需求上有所不同。系统必须能够有效处理三种关键类型的工作负载: CPU和IO密集型、内存密集型和带宽密集型。

## 通过更好的SSD解 决挑战—— ScaleFlux CSD3000

#### CSD3000是什么?

ScaleFlux CSD3000 在IO、延迟和存储成本效益方面相较于传统的NVMe SSD实现了显著的改进。除了企业级NVMe SSD应具备的功能外,CSD3000将硬件数据压缩引擎直接集成到SSD控制器中。这一创新设计将数据压缩的潜力转化为了性能、耐用度和经济效益的大幅提升。

### EDA数据可以压缩吗?

ScaleFlux 对EDA流程的各个阶段进行了压缩比的测量,结果显示:

- 设计与仿真阶段的压缩比达到了10:1

- 综合阶段的压缩比为7:1

- 物理设计阶段的压缩比则为2:1

### 有哪些优势?

- **IOPS超过其他存储设备的2倍** → 更高效 地利用CPU,减少延迟,缩短仿真运行时间。

- **有效容量超过2倍** → 每TB SSD可存储2 倍数据,降低存储成本。

- 在混合工作负载下性能提升最高可达4

倍→能够平稳地处理任何读写混合,

以支持EDA各阶段的性能。

- 在高强度I/O负载下保持极其稳定的延迟迟→避免延迟峰值影响仿真运行。

EDA阶段:工作负载和数据类型